函数调用链:

1 | type_init(xio3130_upstream_register_types) -> type_register_static(&xio3130_upstream_info); -> xio3130_upstream_class_init(ObjectClass *klass, void *data) |

pci 设备主要有两个成员变量–DeviceClass、PCIDeviceClass

初始化这个两个成员变量的过程如下:

1 | static void xio3130_upstream_class_init(ObjectClass *klass, void *data) |

xio3130_upstream 有一个父类————PCIEPort,从

1 | static const TypeInfo xio3130_upstream_info = { |

就可以看出来。同理可以看出来 PCIEPort的父类是PCIBridge,PCIBridge的父类是抽象类PCIDevice。

PCI 设备寄存器初始化过程

pci 设备类的定义

1 | //pci 物理设备的空间 |

instance_size 和 class_size 的区别在于它们分别定义了对象和类的内存大小。对象通常存储设备的状态和属性,而类则包含了类特有的方法和类变量。

pci_device_class_init 函数中注册了实例化函数,当需要实例化pci设备时就会分配一个instance_size大小的空间。

pci bridge 写配置

pci_bridge_write_config 调用了 pci.c 里面的 pci_default_write_config实现设备网桥设备的读写。pci_default_write_config函数内容如下:

1 | void pci_default_write_config(PCIDevice *d, uint32_t addr, uint32_t val_in, int l) |

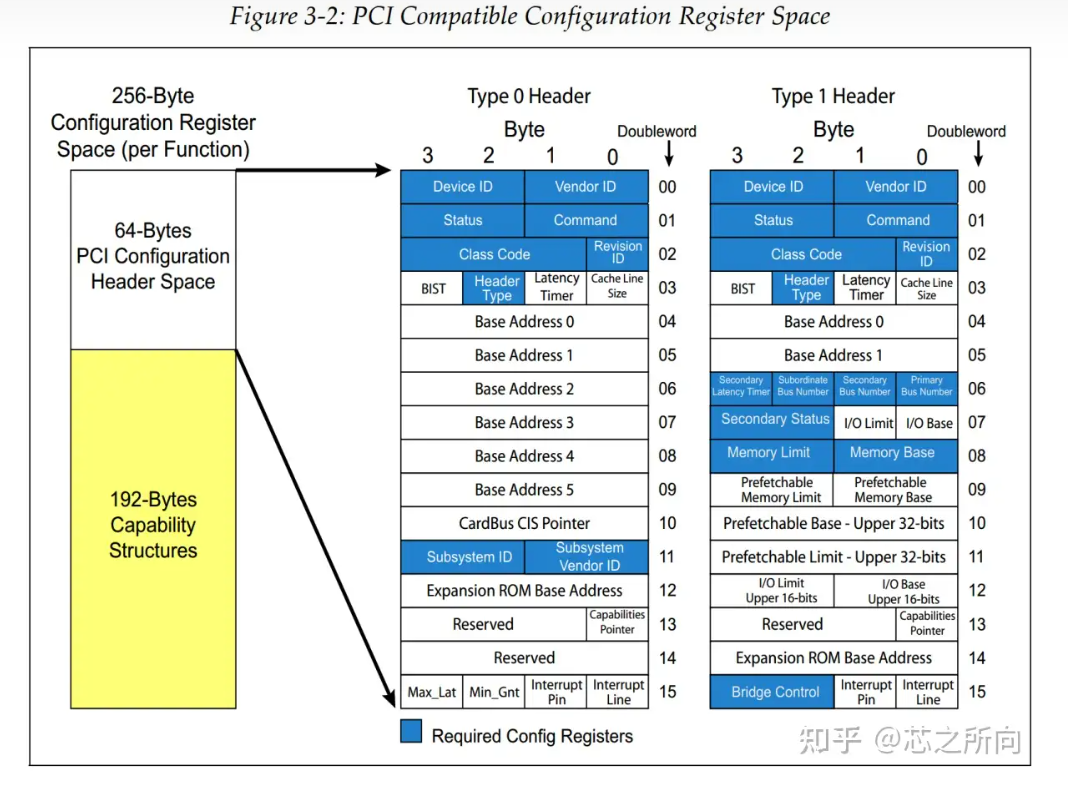

d->config是pci设备配置空间,为了方便,这里贴出地址空间的图片可以对应上。